74hc161 Ic Presettable Synchronous 4 Bit Binary Counter Asynchronous Reset

₨ 100

The 74HC161 is a synchronous presettable binary counter with an internal look-ahead carry.

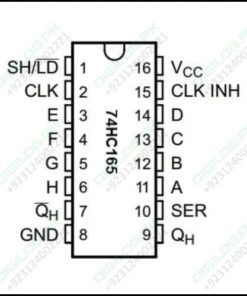

Synchronous operation is provided by having all flip-flops clocked simultaneously on the positive-going edge of the clock (CP). The outputs (Q0 to Q3) of the counters may be preset HIGH or LOW.

A LOW at the parallel enable input (PE) disables the counting action and causes the data at the data inputs (D0 to D3) to be loaded into the counter on the positive-going edge of the clock. Preset

takes place regardless of the levels at count enable inputs (CEP and CET). A LOW at the master reset input (MR) sets Q0 to Q3 LOW regardless of the levels at input pins CP, PE, CET and CEP

(thus providing an asynchronous clear function).

The look-ahead carry simplifies serial cascading of the counters. Both CEP and CET must be HIGH to count. The CET input is fed forward to enable the terminal count output (TC). The TC output thus enabled will produce a HIGH output pulse of a duration approximately equal to a HIGH output of Q0. This pulse can be used to enable the next cascaded stage. The maximum clock frequency for the cascaded counters is determined by the CP to TC propagation delay and CEP to CP set-up time.

Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

Features:

- Complies with JEDEC standard no. 7A

- CMOS input levels

- Synchronous counting and loading

- Two count enable inputs for n-bit cascading

- Asynchronous reset

- Positive-edge triggered clock

- ESD protection:

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- Multiple package options

- Specified from -40 °C to +85 °C and -40 °C to +125 °C

Applications:

- Presettable synchronous 4 bit binary counter

DataSheet:

Package Includes:

- 1 x 74hc161 IC

Be the first to review “74hc161 Ic Presettable Synchronous 4 Bit Binary Counter Asynchronous Reset” Cancel reply

Related products

DLD LAB CMOS , IC'S , Components

DLD LAB CMOS , IC'S , Components

DLD LAB CMOS , IC'S , Components

DLD LAB CMOS , IC'S , Components

7 Segment Display

7448 Bcd To 7 Segment Decoder Driver Ic 74ls48 Sn74ls48n 74hc48

DLD LAB CMOS , IC'S , Components

DLD LAB CMOS , IC'S , Components

DLD LAB CMOS , IC'S , Components

Reviews

There are no reviews yet.